正文

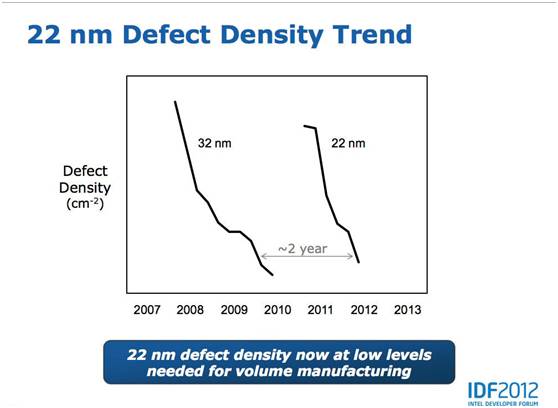

当然,晶圆厂会不断完善和改进工艺,D0一般从刚开始研发到成熟量产的两年过程中会不断降低。下面请看32nm和22nm工艺当初的D0发展趋势。

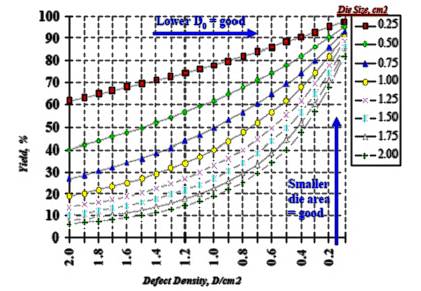

问题来了,良率只和D0有关吗?

非也非也!我们再回到那个夹馍,100个肉丁里,有一个是坏的。如果我们切100份,坏的肉丁影响了一份,那么良率就是99%。如果我们把馍切1000份呢?那么那个坏的肉丁还是只影响一份,但这时良率就变成99.9%了。我们把每一份想象成一个芯片,那么芯片的面积越大,良率就越低。其实,换句更通俗的话讲,这和战争中胖子比瘦子更容易中弹是一个道理吧。请看下图关于D0、芯片面积和良率的关系:

关于神奇的D0,讲到这里结束了吗?还没有哦,大家要注意,对于芯片里Logic(逻辑)电路和SRAM(静态存储器)电路,D0是不一样的!为什么呢?因为SRAM的密度要比Logic大得多,那么同样是掉一颗缺陷,落在Logic区域的,可能就掉在空地上了,而掉在SRAM区域的,很可能影响电路。所以,晶圆厂针对Logic和SRAM提供不同的D0值,在预测目标良率的时候要根据芯片里面SRAM和Logic的面积比例综合考量哦。

试想,如果天上掉下来一颗石头,哪里伤亡更惨重呢?

二、产品设计方法

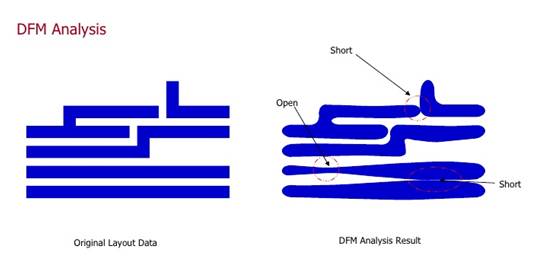

这里讲的设计方法,和良率息息相关的主要是可制造性设计(DFM)和可测试化设计(DFT)。可制造性,顾名思义,就是设计的时候要考虑到制造的因素。同样一个设计,版图不同的画法、元器件摆放方向、位置,都有可能影响到最终的良率。这是当工艺越来越先进,线宽越来越小时所带来的不可逃避的问题。

一般情况下,当工艺进入65nm及以下,晶圆厂就会提供可制造性设计规则供IC设计公司检查。但是一般认为65nm及45nm工艺,可制造性设计规则是供参考的。因为工艺足够成熟,可以不必在设计上花费很大的精力去遵守可制造性设计规则。但是到了28nm及以下,可制造性规则就是必须在设计过程中严格遵守了。

DFT比较复杂,避免把大家讲糊涂,这里就先不详述了。

三、测试方法

首先,需要强调一下,测试方法不会改变芯片本身的质量,不会因为不同的测试方法,将本身一个功能失效的芯片变成好的芯片。但是,经过优化的测试方法,可以在具有高测试覆盖率的前提下,控制成本又能降低在最终客户那里的DPPM(Defective Parts Per Million,表征质量的参数),减少退货率。

晶圆生产出来后,在出晶圆厂之前,要经过一道电性测试,称为晶圆可接受度测试(WAT)。这个测试是测试在切割道(Scribe Line)上的测试键(TestKey)的电性能。测试键通常设计有各种原件,例如不同尺寸的NMOS、PMOS、电阻、电容以及其他工艺相关的特性。这一道可以当做是初选。那些有严重生产问题从而使得测试键的电性能超出规格之外的晶圆会在这一道被筛选出来,报废掉。这一道报废掉的晶圆,因为还没有出货到客户手里,所以是不收取客户钱的,由晶圆厂自己吸收。

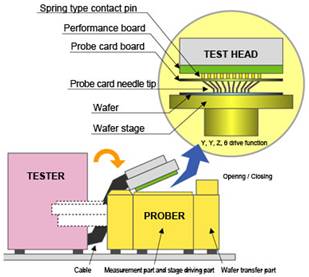

WAT测试结束后,晶圆工艺就算完成。下一步就是来到测试厂这里进行测试。第一道晶圆切割前的测试我们称为CP (Chip Probing), 因为这一道测试是在完整的晶圆上测的,用到的机台,我们称作Prober。每一个产品,都会有针对自己设计的Prober Card, 上面根据芯片的测试焊盘(Pad)的位置装有对应的测试探针及电路与测试台连接。每次测的时候,测试头从上面压下来,探针就会扎到Pad上,然后供电进行测试。