正文

AP和外设连接的高速数字总线

MIPI

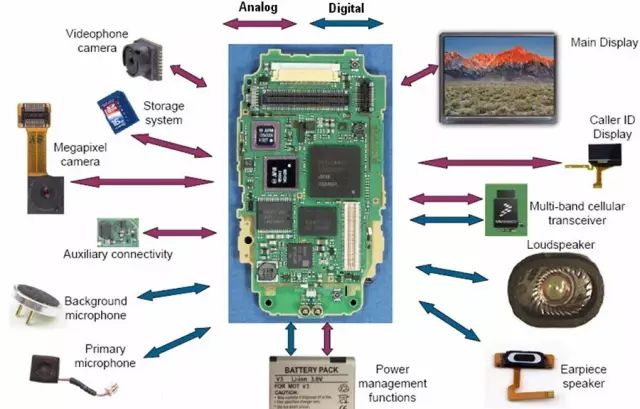

对于现代的智能手机或 PAD 来说,其内部要塞入太多各种不同接口的设备,给手机的设计和元器件选择带来很大的难度。其内部存储、显示、摄像、声音等内部接口都是各不相同的。即使以摄像头接口来说,不同的摄像头模组厂商也可能会使用不同的接口形式,这给手机厂商设计手机和选择器件带来了很大的难度。

MIPI (Mobile Industry Processor Interface)

是 2003 年由 ARM, Nokia, ST ,TI 等公司成立的一个联盟(www.mipi.org),目的是把手机内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。

MIPI 联盟下面有不同的 WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口 CSI、显示接口 DSI、射频接口 DigRF、麦克风/喇叭接口 SLIMbus 等。统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。

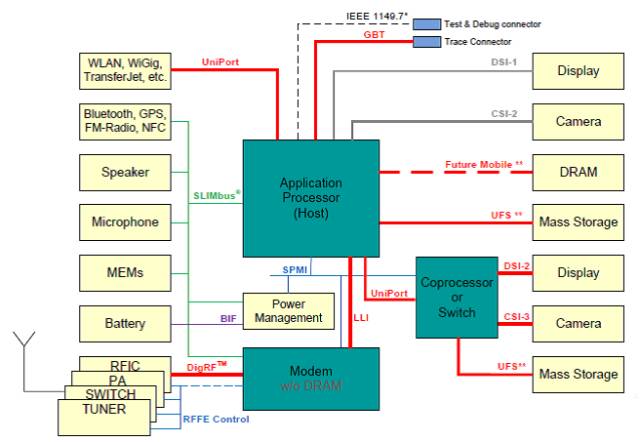

MIPI 组织主要致力于把移动通信设备内部的接口标准化从而减少兼容性问题并简化设

计。下图是按照 MIPI 组织的设想未来智能移动通信设备的内部架构。

目前已经比较成熟的 MIPI 应用有摄像头的 CSI 接口、显示屏的 DSI 接口以及基带和射频间的 DigRF 接口。UFS、LLI 等规范正在逐步制定和完善过程中……

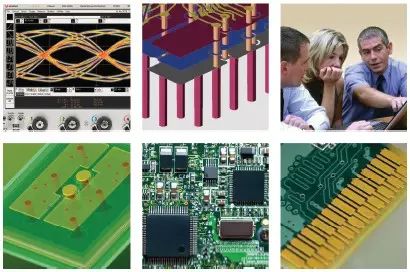

而由于 MIPI D-PHY 的信号比较复杂,虽然 CSI-DSI 接口已经比较成熟,但想要保证接口信号和协议的一致性仍需要很复杂的测试。为了大家能够全面了解 MIPI CSI-DSI 信号和协议的测试方法,特奉上一段 MIPI D-PHY 实际测量视频。本视频集中讨论了 MIPI D-PHY 技术和测试,当然生活不止眼前的 D-PHY,还有远方的 M-PHY(有完没完

😭

),然后继续 M-PHY……

▲

建议在WiFi环境下观看视频,土豪请随意

若您从事智能手机或平板等的研发,我们还可提供测试验证的一揽子方案资料,包括基于协议分析仪而不是示波器的协议分析,微安级的电流测试等。欢迎登录

Keysight官网

查看相关资料。

(二)

现在智能手机芯片主流内存都采用了

LPDDR4

它到底好在哪里呢?

大鲸鱼、大鲸鱼

小编念念不忘的

内存大鲸鱼

它和CPU之间是怎么连接的呢?

答案就是 –

LPDDR4

LPDDR4 和她的亲姐妹DDR4 和组成了最新一代的双倍数据速率(DDR)SDRAM 存储器,

与 LPDDR3和DDR3相比,数据速率翻倍,2400 Mb/s已算不上高速,LPDDR4 规范中的最大数据速率已达 4266 MT/s。

除了性能有明显增强外,DDR4 和 LPDDR4 还增添了许多新特性,在体系结构上也有所改变,由此获得了众多优势,尤其是在降低功耗方面:

与 DDR3 和 LPDDR3 相比 ↘↘↘

-

节能 30-40%

-

更高效率和可靠性

-

更高的密度

-

更多误码检测

这些优势使芯片拥有

更小的体积,更加节能,

同时散热更少

总之一句话

当然,毫无悬念的,它也变得更复杂了,测试起来,嘿嘿,也更难了,您知道吗?

(悄悄地告诉你

当 DDR4 速率超过2400MT/s后,是德科技的逻辑分析仪进入技术无人区,目前是这个星球上可完成协议测试的唯一逻辑分析仪方案噢。

)

当 DDR4 速率超过2400MT/s后,是德科技的逻辑分析仪进入技术无人区,目前是这个星球上可完成协议测试的唯一逻辑分析仪方案噢。

)

撇开LPDDR4高速电路的设计不谈

(为什么不谈?因为在下面的视频里会谈的特别细……)

LPDDR4的测试,分为物理层测试和功能验证两部分。

JEDEC 标准要求用户分离读/ 写数据以进行数据验证。根据 DDR4 JEDEC 规范,需要采用不同的模板对眼图进行测试,以确保有足够宽的裕量窗口用于无差错数据传输。

这些就是 Rx 计时窗口(TdlVW)测试和 Rx 模板电压(VdlVW)测试。进行这些测试之前,必须能够先把读取数据和写入数据分开。

与大多数串行标准不同,在 DDR 中,读和写是在同一时间通过总线。因此,必须知道哪些数据块与读相关,哪些与写相关。

在以前的 DDR3 技术中,读和写可以分开,因为二者的突发脉冲前导码型不同。在数据开始转换之前,读前导码型由 Hi-Z 状态变为低状态,保持约四分之一到半个时钟周期;写前导码型则由 Hi-Z 状态变为一个时钟周期 。对于 DDR3 工程师而言,有了前导码的差异,识别读写周期就相当容易。

然而……