正文

光刻

由于双重曝光成为关键金属层(即20nm处的金属1和金属2)的要求,大多数专家认为,器件缩小的主要限制因素是光刻。

幸运的是,芯片制造商已经能够扩展传统的光刻技术。使用各种多重曝光工艺,芯片制造商能够分开掩模和图案。这种方法可以将今天的193nm波长的光刻技术扩展到16nm / 14nm,10nm甚至7nm。

但是在7nm或5nm处,图案复杂性和掩模计数正在成为浸入式和多重曝光的限制因素。28nm器件具有40至50个掩模层。相比之下,14nm / 10nm器件具有60层,预计7nm可以跃升到80到85层。在5nm可以有100层。

为了简化7nm/5nm的工艺流程,芯片制造商一直在等待极紫外(EUV)光刻技术,这是一种13.5nm波长的技术。EUV预计为45nm,但遇到了一些仅仅在最近才刚刚解决的问题。随着光源的增强,产量持续上升,EUV似乎终于接近了商业化生产。

极紫外光刻技术是否接近大批量生产还有待观察。 ASML的EUV服务和产品营销副总裁Hans Meiling表示:“我们的工厂每小时生产100个晶圆,今年晚些时候将提高到每小时125个晶圆。”

同时,根据11个月平均数,正常运行时间已经提高到80%以上。Meiling表示是90%+,这与浸入式光刻相当。事实上,我们已经达到了这一点,但并不令人震惊。这个项目看起来就像科幻小说中的内容。

这里有一些工程技巧。首先是从小液滴中得到稳定的锡液滴。这些小液滴被激光击中。然后,激光再次发射,这次是主脉冲。主激光脉冲击中薄饼状锡液滴并使其蒸发,转而将它变成等离子体。等离子体发射13.5nm波长的EUV。

“每秒有5万个液滴,”Meiling说,“这是一个受控的过程。它们以每秒数百米的速度流进去。然后我们将CO²激光射入每个液滴。因此,CO²激光器的速率与液滴发生器相同。每个液滴都变成了薄饼。由于CO²的作用,它膨胀成为200-400微米的雾滴,而不再是固体。第一个脉冲使它成为了薄饼。”

图1:跟随反弹光。(来源:ASML)

更令人震惊的是,这是有效的。有越来越多的论文可以证明这一点。

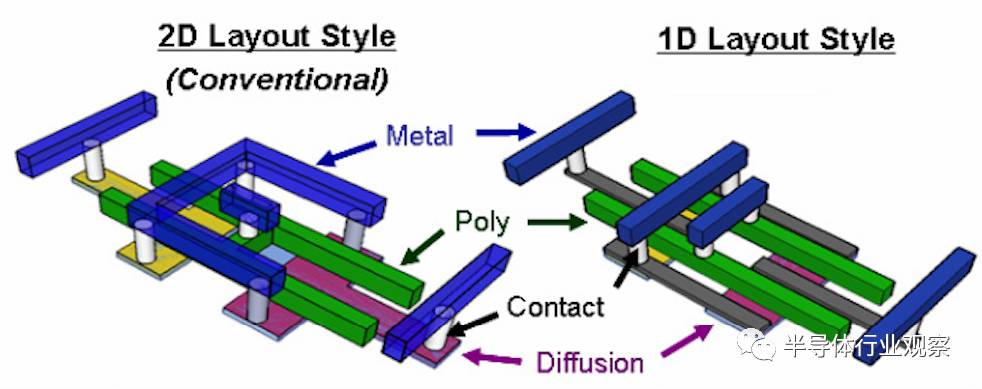

但是,尽管在光刻方面有这些改进,但在许多方面,缩小的极限变得越来越明显。每个新节点的布局灵活性都在降低。英特尔能够在45nm转移到1D图形,主要是因为CPU不需要与SoC拥有相同的灵活性水平,它的结构更加规则。对于SoC或ASSP,限制更为明显。

Lam Research首席技术官Yang Pan,说:“我们认为,使用EUV工艺,二维图案会变得太困难。首先,EUV仍然有掩模缺陷问题。我们必须修复这些缺陷,但我们肯定无法一遍又一遍地修复。其次,如果要为EUV获得良好的刻线边缘粗糙度特性,则需要大量能源。目前这是不可能的。所以EUV会走进1D空间。我们此时看不到2D。”

图2:1D vs 2D (来源:Multibeam公司)

EUV工艺还存在很多限制。Applied Materials蚀刻业务部副总裁兼总经理Raman Achutharaman说:“主要的是EUV的解决方案。它没有解决定位误差的要求。其二,随着较长的EUV的推出,甚至EUV也需要多重曝光。对于切割和通孔,可以使用EUV。但是对于线和空间,你只能使用基于空间的方法。”