正文

目前流行的

MOS

管模型大致可分为两类,一类是基于阈值电压(

Threshold Voltage-based

)的模型,典型的代表为

BSIM3

和

BSIM4

,大家可以参阅

Razavi

的课本。它的一个典型特征就是阈值电压是

Vsb

的函数,以此来刻画体效应。这一类模型在深亚微米工艺下有较大的局限性。另一类基于电荷(

Charge-based

)的模型,其代表为

BSIM6

和

EKV

模型。

BSIM6

模型是现在仿真工具中的

CMOS

工艺的标准模型(

2013

年发布)。而

Abidi

教授在课堂上讲述的

EKV

模型,能够在手算过程中提供很多设计指导。(

EKV

,由其三位发明者

Enz

,

Krummenacher

,

Vittoz

的名字首字母命名)

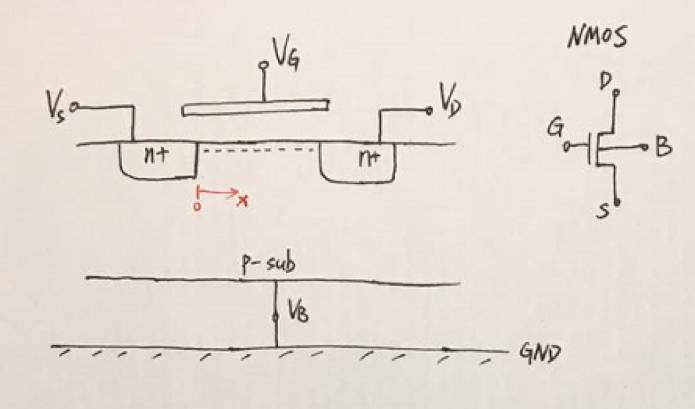

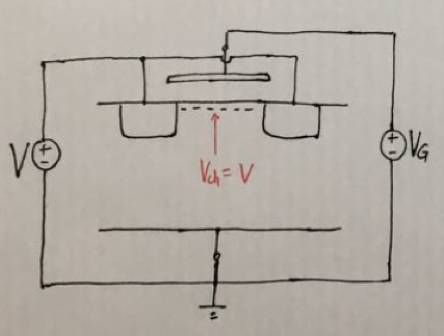

如下图所示是一个

NMOS

的模型图。

MOS

管是四端器件,包括源端(

S

)、漏端(

D

)、栅端(

G

)和衬底(

B

)。在标准

CMOS

工艺中,所有

MOS

管共用一个

P

型衬底,为了防止

PN

结正偏,

P

型衬底一般接

GND

。

Vs

、

VD

、

VG

均相对于衬底电压定义。源极和漏极完全对称,逐渐增加栅极电压,在器件表面会出现反型层,对于

NMOS

来说,反型层由电子组成。反型层非常薄,其厚度可以近似忽略不计(

Charge-Sheet Approximation

),因而在分析中我们采用简单的一维模型。在图中以源极为原点,由源极引向漏极画出

x

轴。

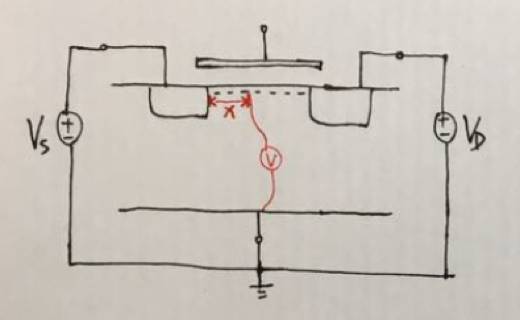

如下图所示,我们将坐标为

x

处反型层的面电荷密度记为

Q

inv

’(x)

,该处的沟道电压(相对于衬底)记为

V

ch

(x)

,

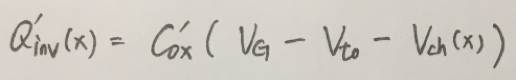

栅极、反型层和夹在中间的栅氧化层可以看出一个平行板电容器,则反型层面电荷密度与两极板间的电压的关系如下:

下面我们定义两个重要的概念:夹断电压(

V

p

, pinch-off voltage

)和阈值电压(

V

t0

, threshold voltage

)。在下图中,源极和漏极保持等电位,这样整个沟道的电势相同。如果固定

V

G

,当沟道电压增加至

V

p

时,反型层电荷密度减为

0

;如果固定沟道电压为

0V

,当

V

G

减为

V

t0

时,反型层电荷密度减为

0

。这里的阈值电压

V

t0

是定义在整个沟道等电位且电位为

0

的条件下,因而是一个定值,与之形成对比,传统模型中的阈值电压

V

TH

是

V

sb

的函数。另外值得注意的是,夹断电压

V

p

的定义不只在源极漏极等电位使才有效,只要沟道中某一点的电压

V

ch

(x)

大于

V

p

,在该点处沟道就会被夹断。

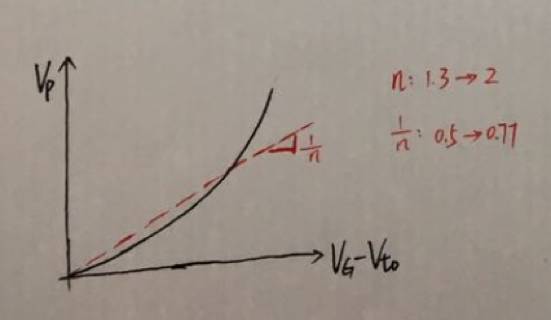

夹断电压和栅极电压的关系如下图所示,这种非线性是由反型层下方的势垒电容

C

dep

的非线性造成的(在介绍

MOS

管电容模型时我们会详细阐述)。为了简化模型,通常用一条斜率为

1/n

的直线来近似,即

V

p

= (V

G

-V

t0

)/n

。在之后的计算中我们采用

n = 1.5

。

注意:有的时候

V

p

与

VG-V

t0

的非线性关系会导致大信号偏置电路无法工作,具体地说,就是我们会推出

n

既大于

1

,又小于

1

,说明联立不等式无解。这个例子我们会在之后介绍偏置电路的时候举一个例子。

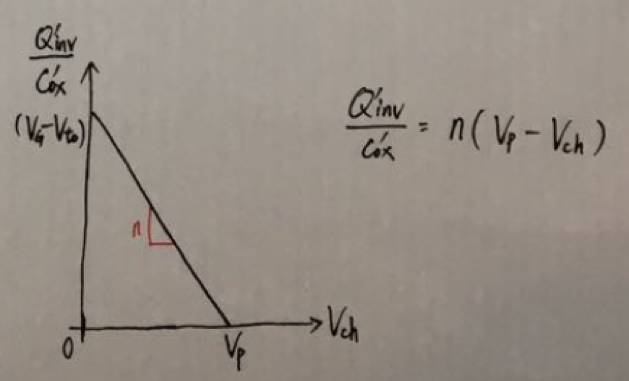

根据以上的近似,可以画出

Q

inv

’

和

V

ch

的关系。当

V

ch

= V

p

时,沟道被夹断,电荷密度为

0

;当

V

ch

= 0

时,

Q

inv

’= C

ox

’*(V

G

– V

t0

)

。细心的童鞋们可能已经注意到,下图的关系式与之前所列的平行班电容器的公式略有偏差,原因就是之前的公式是在忽略势垒电容

C

dep

的效应,或者说在

n= 1

的条件下推出的。

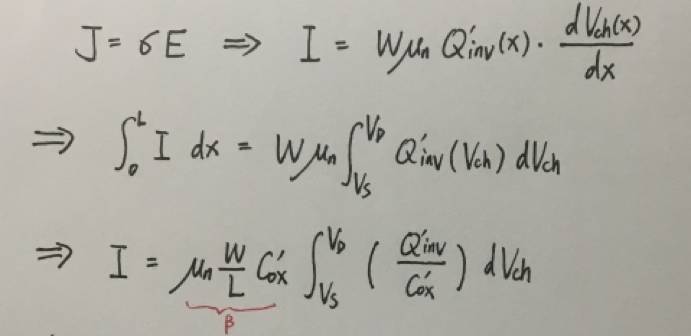

有了上面的铺垫,我们接下来推导电流的公式