正文

图1 Sony三层堆叠式CMOS图像传感器的芯片横截面

然而,我们似乎是超之过急了,因此,让我们先来看看Sony的新闻稿以及在ISSCC发表的论文细节吧!

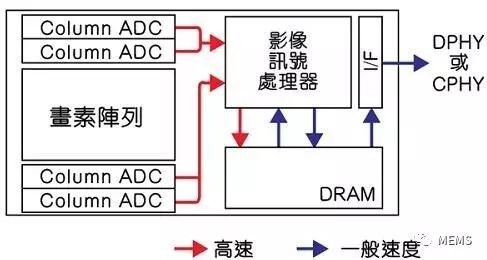

图2 Sony CMOS图像传感器的信号路径方块图

Sony在其较早的1930万像素图像传感器中使用双模拟/数字转换器(ADC),为像素信息进行数字化。而今,该公司使用4层ADC的结构提高读取速度,同时也改善了处理能力。DRAM则用于暂时储存高速资料,然后再以传感器接口的最佳速率输出。该设计使其能以1/120秒读取1930万像素的静态图像,而在影片模式下可达到1000fps的画面更新率,较以往产品的静态图片与动态影片分别提高了4倍和8倍的速度。

由于在CIS和ISP之间加进了DRAM夹层,高速资料必须经过存储器芯片才能到达ISP,然后再以适于应用处理器的常规速度,来回传送直到经由ISP的I/F接口区块进行输出。

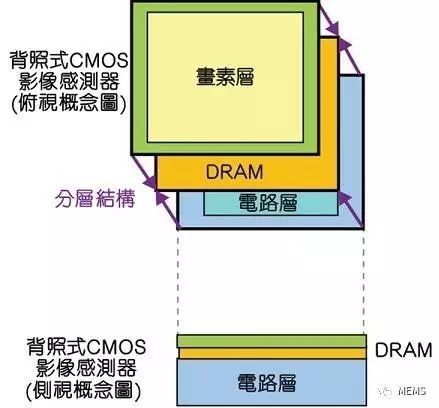

图3 Sony新开发配备DRAM的三层堆叠式CMOS图像传感器

图3是这种传感器运作原理的精简版;但在Sony发表的论文中有更详细的介绍,包括960fps如何成像以及慢动作的工作原理

根据该论文解释,像素阵列位于裸晶的顶层,DRAM阵列和列驱动器位于中间,其余的区块则位于底部的ISP裸晶。我们尚未取得这三层裸晶的照片,但该论文中提供了一些图片。