正文

4、离子注入

离子注入 --- 尺寸:晶圆级(大约300毫米/12英寸)

覆盖着光刻胶的晶圆经过离子束(带正电荷或负电荷的原子)轰击后,未被光刻胶覆盖的部分嵌入了杂质(高速离子冲进未被光刻胶覆盖的硅的表面),该过程称为掺杂。由于硅里进入了杂质,这会改变某些区域硅的导电性(导电或绝缘,这依赖于使用的离子)。这里展示一下空洞(well)的制作,这些区域将会形成晶体管。

[注:据说这种用于注入的带电粒子被电场加速后可达30万千米/小时]

去除光刻胶--- 尺寸:晶圆级(大约300毫米/12英寸)

离子注入后,光刻胶被清除,在掺杂区形成晶体管。

晶体管形成初期 --- 尺寸:晶体管级(大约50~200纳米)

图中是放大晶圆的一个点,此处有一个晶体管。绿色区域代表掺杂硅。现在的晶圆会有几千亿个这样的区域来容纳晶体管。

5、刻蚀

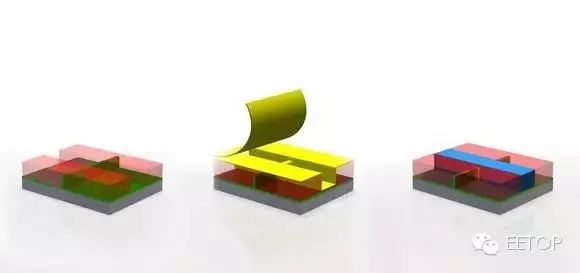

刻蚀 --- 尺寸:晶体管级(大约50~200纳米)

为了给三门晶体管制造一个鳍片(fin),上述光刻过程中,使用一种称为硬膜片(蓝色)的图像材料。

然后用一种化学物质刻蚀掉不想要的硅,留下覆盖着硬膜片的鳍片。

6、临时门的形成

二氧化硅门电介质 --- 尺寸:晶体管级(大约50~200纳米)

在光刻阶段,部分晶体管用光刻胶覆盖,把晶圆插入到充满氧的管状熔炉中,产生一薄层二氧化硅(红色),这就造就了一个临时门电介质。

多晶硅门电极 --- 尺寸:晶体管级(大约50~200纳米)

在光刻阶段,制造一层多晶硅(黄色),这就造就了一个临时门电极。

绝缘 --- 尺寸:晶体管级(大约50~200纳米)

在氧化阶段,整个晶圆的二氧化硅层(红色透明)用于跟其它部分绝缘。

英特尔使用”最后门” (也称为 “替代金属门”)技术制作晶体管金属门。这种做法的目的是确保晶体管不出现稳定性问题,否则高温的工序会导致晶体管不稳定。

7、“最后门” 高K/金属门的形成

[注:介电常数K为高还是低是相对的,但英特尔的标准跟业界不同,业界普遍采用IBM的标准,用低K介质能减少漏电流,但是加工困难,目前大规模数字电路多用高K介质。]

牺牲门的去除 --- 尺寸:晶体管级(大约50~200纳米)

用膜片工序里的做法,临时(牺牲)门电极和门电介质被刻蚀掉。真实门现在就会形成了,因为第一门被去掉了,该工序称为“最后门”。

高K电介质的使用 --- 尺寸:晶体管级 (大约50~200纳米)

在称为”原子层”沉积的过程中,晶圆表面覆了一层分子。图中黄色层代表这些层中的两层。使用光刻技术,在不想要的区域(例如透明二氧化硅的上面)里,高K材质被刻蚀掉。

金属门 --- 尺寸:晶体管级 (大约50~200纳米)

晶圆上形成金属电极 (蓝色),不想要的区域用光刻的办法刻蚀掉。 跟高K材料配合(薄薄的黄色层)起来使用,可以改善晶体管性能,减少漏电流的产生,这是使用传统的二氧化硅 / 多晶硅门不能企及的。

8、金属沉积

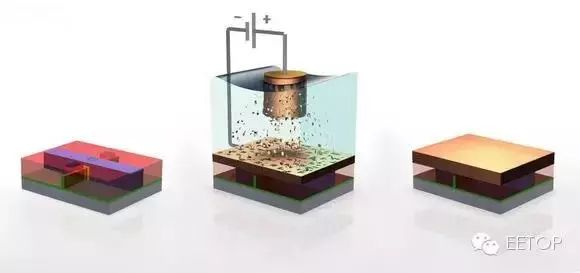

晶体管就绪 --- 尺寸:晶体管级 (大约50~200纳米)

晶体管的建造快竣工了。

晶体管上方的绝缘层刻蚀出3个小洞,这3个洞里被填充上铜或其它材质,以便跟别的晶体管导通。

[注:晶体管也就是通俗意义上的三极管,需要3个引线脚,所以一个晶体管的绝缘层上得刻蚀出3个小洞]

电镀 --- 尺寸:晶体管级 (大约50~200纳米)

在该阶段,晶圆浸在硫酸铜溶液里,作为阴极,铜离子从阳极出发到达阴极,最后铜离子会沉积在晶体管表面。

电镀后序 --- 尺寸:晶体管级 (大约50~200纳米)

经过电镀,铜离子在晶圆表面沉积下来形成薄薄的一层铜 。

9、金属层

抛光 --- 尺寸:晶体管级 (大约50~200纳米)

多余的材质会被机械抛光,直到露出光亮的铜为止。

金属层 --- 尺寸:晶体管级(6个晶体管组合起来大约500纳米)

构造多重金属层以一种特殊的结构来导通(请考虑宏观世界中的“导线”)晶体管,这些“导线”怎么连接,要由某个型号处理器(例如第2代英特尔Core I5处理器)的架构师和设计团队来决定。

尽管计算机芯片看上去十分平整,其实可能会超过30层,是一个十分复杂的电路。 一个放大的芯片看上去是由电线和晶体管组成的错综复杂的网络,该网络看上去像将来某天地面上建造成的多层高速公路系统。